# MLDL2000 Design Specifications

# **Introduction**

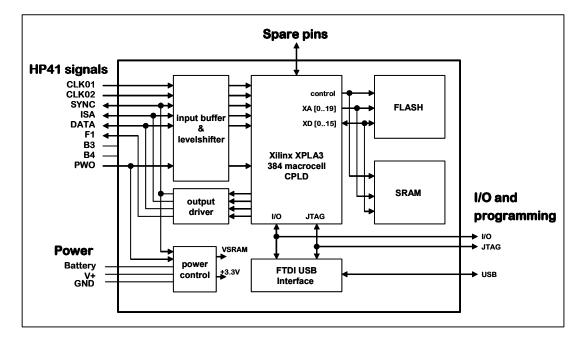

The MLDL2000 is a Machine Language Development Lab (MLDL) for the HP41 series of calculators with large amounts of EPROM and SRAM. The basic principle is loosely based on the classic MLDL as published in the PPC Journal, V9N3 in the article by Lynn A. Wilkins. This design will be referenced to as the 'Classic MLDL'. Added is an I/O Interface to exchange data with a PC and modified interfacing with the actual memory devices. This specification serves as a description for the HP41 bus as well and touches upon several issues like bank switching and other topics that are relevant for the design and use of the MLDL2000. The CPLD based MLDL2000 allows changing, expanding or upgrading the functionality.

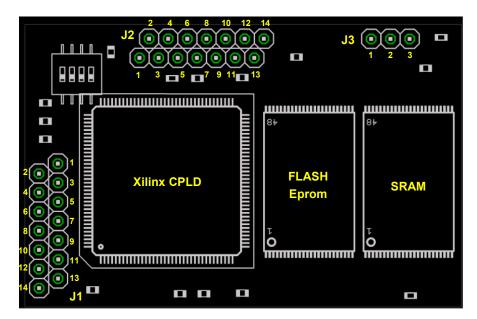

As the name implies, the project started just before the turn of the century. Available time limited the amount of work that could be done on the project, but the start of the basic thinking and collecting information dates from the end of 1999. The design is based on a Xilinx programmable device. A prototype environment was purchased in December 2002, based on a 256-macrocell XPLA3 device from Xilinx. The final MLDL2000 is realized with a 384 macrocell device.

In May 2003 the first prototype of the MLDL2000 was running. The implementation was based on a simple ROMBox application, with support of only one bank of the traditional L8 and U2 EPROMs. The prototype setup was tested with a 2\* speeded HP41C and an unmodified HP41CX. A more advanced prototype resembling the final product was done in January 2004, and the final PCB's were received in November 2004. Beta's were made in February 2005. First shipments out of production were done in July 2005. Preparations are underway for a new version 2 of the MLDL2000.

All information about the MLDL2000 is published on my website and is public under the GPL license conditions. Working devices will be offered on the free market against reasonable cost, with the objective to make the MLDL2000 available to the HP41 user community on a non-commercial base. This specification is intended to be a source of information and to understand how the MLDL is working. A separate User Manual is available to explain the actual use of the MLDL2000.

#### Meindert Kuipers

September 2008

#### **References and credits**

- VHDL for Programmable Logic, book by Kevin Skahill

- Museum of HP Calculators, website by David Hicks

- HP41 Archive website, by Warren Furlow

- Inside the HP41C, article by Kelly McLellan

- HP41 Bus Interfacing, article by Jim De Arras

- HP41 Machine Language Development Lab, article by Lynn A. Wilkins

- HP41C/CV/CX Technical Manual

- Xilinx tools, datasheets, application notes en support site

- Diego Diaz for his cooperation and his Clonix and NoVRAM modules

- Many individual contributors for their tips and encouragement

- FTDI USB interface IC FT2232C

There is no particular order of importance intended.

#### **Conventions**

- 00FF Hexadecimal numbers are used to indicate addresses, leading zero's are typically used to indicate the total possible range, e.g. 00FFFF. The 'x' character is used for a "don't care" situation

- \$040 The '\$' character is used to indicate hexadecimal values when context is not clear

- 170 Octal values are indicated with the character 'o' after the value

- %1010 Binary values are preceded with the '%' character, the 'x' character is used for don't care bits

- /OE Signal names preceded by a slash ("/") indicate that this signal is either active low or that it becomes active at a falling edge. 'Asserted' or 'active' in this case means that the signal is low or logic '0';

- in/out Signal directions generally refer to the MLDL2000 assembly or CPLD, "in" meaning "to the MLDL2000", "out" meaning "coming from it"

- HP41 HP41 indicates all versions of the HP41 calculator, including HP41C, CV, CX, etc

www.hpmuseum.org www.hp41.org PPC Calculator Journal V6N7 PPC Calculator Journal V7N3 PPC Calculator Journal V9N3 www.hp41.org www.xilinx.com

www.ftdichip.com,

ISBN 0201895730

Email: meindert@kuiprs.nl

Website: www.kuiprs.nl

# **Copyrights and Disclaimer**

© Copyright 2005-2008 by Meindert Kuipers, The Netherlands

This document, the MLDL2000 design, VHDL code and software are copyrighted under the GNU General Public License. This means that anyone is free to use the design for his or her own purposes and may modify it. The MLDL2000 and accompanying software is supplied "as is" without warranty of any kind nor do I assume any kind of liability including consequential damages. The specifications, functionality or contents may be changed without notification to the user. If you wish to incorporate (parts of) the design into products which are distributed under any other conditions than the GNU Public License (commercial on non-commercial) you will have to have permission from the author. Please make certain that you have read and understood the GNU General Public License if you plan to use (parts of) the design.

Note that some parts of the MLDL2000, specifically the USB interface and driver software, are commercially licensed but free (without source code). Any license fees should be handled directly with the manufacturer. The development software for the Xilinx devices is basically free but requires registration with Xilinx. The application software controlling the USB module is written in Borland Delphi, the compiler must be licensed. All brand or product names are trademarks or registered trademarks of their respective holders.

Information in this document has been carefully checked and is believed to be accurate as of the date of publication; however, no responsibility is assumed for inaccuracies. I will not be liable for any consequential or incidental damages arising from reliance on the accuracy of this document. The information contained herein is subject to change without notice.

### **Table of Contents**

| Introduction                                             |    |

|----------------------------------------------------------|----|

| References and credits                                   | 1  |

| Conventions                                              | 1  |

| Copyrights and Disclaimer                                | 2  |

| Table of Contents                                        | 2  |

| Scope of the MLDL2000                                    | 3  |

| What is an HP41 MLDL?                                    | 3  |

| MLDL2000 Features                                        | 4  |

| The HP41 interface bus                                   | 4  |

| Signal Timing Description                                | 5  |

| MLDL2000 Operation                                       | 5  |

| MLDL memory layout                                       | 8  |

| Detailed Memory Map                                      | 10 |

| FLASH or SRAM read operation (Typical Instruction Fetch) | 11 |

| SRAM write operation (Typical WROM instruction)          | 11 |

| Bank Switching                                           | 12 |

| External interface                                       | 12 |

| MLDL2000 Hardware Design                                 | 17 |

| Bling-bling your MLDL2000                                | 17 |

| Power Control                                            | 18 |

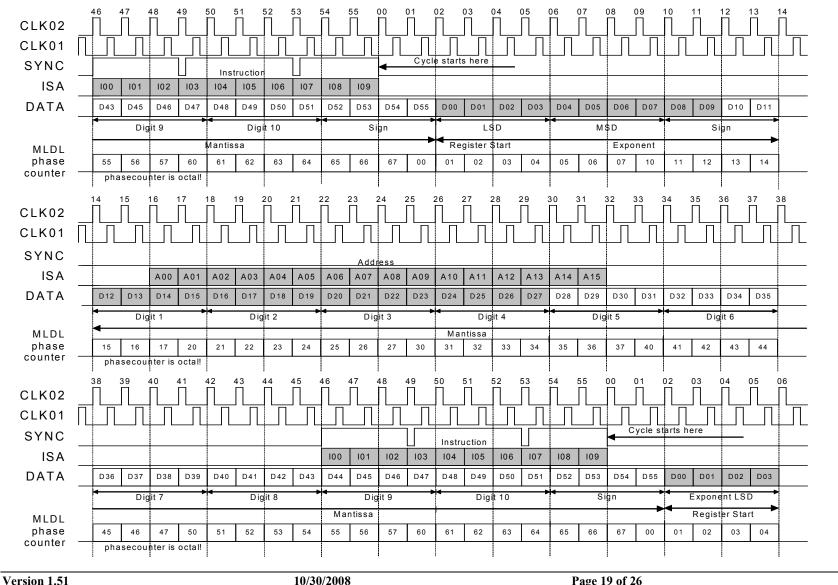

| Appendix A: HP41 Timing Diagram                          | 19 |

| Appendix B: MLDL2000 CPLD pinout for Xilinx XCR3384 CPLD | 20 |

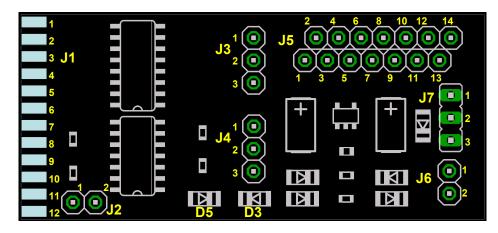

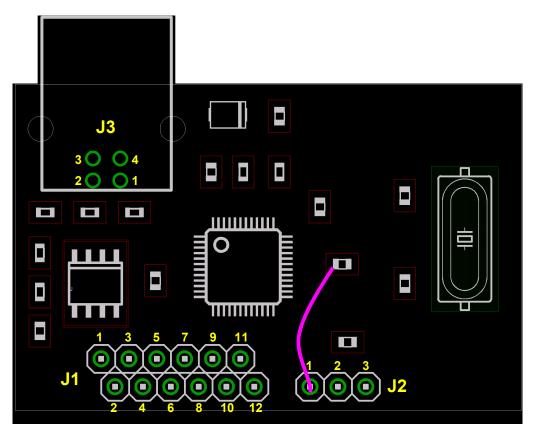

| Appendix C: MLDL2000 Connections and PCB                 | 22 |

| Appendix D: MLDL2000 revision history                    | 25 |

| Appendix E: Errata                                       | 26 |

# Scope of the MLDL2000

My father gave me my first HP21 when I was 15 or 16. This one was quickly upgraded to the programmable HP25. At that time I had a holiday job at a local technical bookstore, which also sold cash registers, computers and ... HP calculators. When the HP41 came out I was quickly there to buy one, as that was very useful in my physics study. Having the '41 I quickly became a PPC member and through a message in the PPC Journal and the local HP dealer I came into contact with a group of other HP41 users. We had regular meetings, and being quite handy with a soldering iron I did many speed upgrades, module doubling (even did one triple module once) and built modules inside calculators. I ruined only one HP41 (my own), but quickly got another one. In the meantime I had built my own Eramco MLDL (bought the PCB's at Eramco and sorted out the rest myself) and had loads of fun with it. I even made my own rom: MEINROM which evolved into the –ML ROM, a co-production with another HP enthusiast.

After many years I decided to wipe the dust off my HP41. I also got myself (through eBay) a HP41CX in very good condition against a reasonable price. I downloaded the Xilinx WebISE environment for developing FPGA's and CPLD's and I decided to start using it to implement an MLDL. The Xilinx development environment is free (after registration) and offers a full VHDL suite with timing analyzer and simulator. A 3.3V Xilinx Coolrunner XPLA3 CPLD device is chosen for its low power consumption and possibility to interface directly to 5V CMOS and TTL levels.

I wanted both ROM emulation and MLDL (that is creating ROM) functionality. Combine that with a PC interface and the rough specs (or should I say thoughts) are quickly lined out. Flash EPROM it should be, to prevent use of programmers and UV erasers. SRAM obviously and a flexible interface to the outside world, also needed to get data into and out of the MLDL2000.

The MLDL2000 is my first serious attempt to program a device in VHDL. It will not be perfect and super efficient, but I intend to make it work. I donate the design to the user community for reproduction or improvement, on the condition that no commercial use is being made of the design and that I get all feedback. Users: have fun with it, and let me know!

# What is an HP41 MLDL?

MLDL stand for Machine Language Development Lab. Sounds cool and high-tech, doesn't it? But what does it? The HP41 architecture understands two programming languages: User Code and Machine Code (or M-Code). The latter is normally not available to end-users. Expansion of the HP41 system is usually done with plug-in modules, or ROM (for Read Only Memory). These contain either User Code or M-code (or a mix thereof). These ROMs could be produced by HP only, although larger groups (like the PPC who made the famous PPC ROM) could develop code and have it produced by HP. When details of the HP41 interface became known it was apparent that the ROM could actually be emulated by (battery backed) RAM. An unused HP41 instruction was defined by the user community to enable writing into the RAM and the Machine Language Development Lab was born. It was now possible for end-users to write and test their own M-Code and later burn it into an EPROM.

# MLDL2000 Features

Features of the MLDL2000 are:

- 255 ROM Banks of FLASH EPROM memory, each 4k \* 10 bits, can be relocated to any HP41 ROM location at any bank, including the HP41 System ROMS. Total capacity 1M \* 10 bits

- 64 banks of MLDL SRAM memory, each 4k \* 10 bits, can be relocated to any HP41 ROM location at any bank, including the HP41 System ROMS. Total capacity 512K \* 10 bits (some units have 1M\* 10 bits)

- Bi-directional serial I/O interface, can be relocated to any HP41 ROM location

- Each ROM/RAM block can be individually enabled or disabled

- Non-volatile Settings Registers, with multiple sets of Settings Registers enabled by switches

- USB interface to connect to PC for programming FLASH and SRAM and I/O with the HP41

- FLASH and SRAM memory programmable through PC interface, no eraser or programmer required

- In-System Programmable CPLD as control interface to allow upgrades and/or functional changes (special JTAG programmer cable required, reprogramming over USB a a future upgrade)

- Power consumption about 6-7 mA additional to the HP41 system (typically an HP41CV consumes about 6 mA when no extra modules or peripherals are connected) when running.

Other features may be added as required. In theory it is possible for example to mimic HP41 User Memory (and thus Extended Memory as well) if enough SRAM is available. As the CPLD is fully configurable, other interfaces might be added, like HEPAX support, printer, infrared, etc. Preparations will be taken to allow for these future expansions.

Please note that the user of the MLDL is responsible for the correct settings of the MLDL, as it is rather easy to create conflicts with ROMs sitting at the same address, especially if the HP41 has internal ROMS or if ROMS are plugged into any of the ports.

The MLDL2000 is designed to minimize the number of external parts and to minimize power consumption. The physics of the HP41 interface requires a more complicated circuit for driving the ISA (and DATA) line back to the HP41 in addition to level conversions from the HP41 (around 6 Volt) to the CPLD levels (3.3 Volt)

Minimal part count is important, to enable a version of MLDL2000 to be built in a very small space with a relatively easy layout to fit in a card reader housing.

# The HP41 interface bus

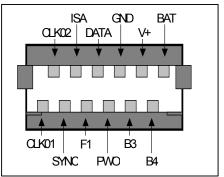

This paragraph offers some background information for understanding the design of the MLDL2000. It is by no means a complete description of the HP41 interface. The HP41 interface bus is a serial bus available on the HP41 I/O ports for plugging in modules and peripherals. Information in this part is mainly based on the article by Jim De Arras in PPC Journal V7N3 and the HP41 Service Manual. The figure shows the signal assignment (view from the front of the module) with the following signals:

CLK01 Phase One Clock: This signal is used to read data on the bus lines and the rising edge of CLK01 qualifies the data on DATA and ISA for reading

- CLK02 Phase Two Clock: This signal is used to count the phases in the processor cycle and to output data to bus lines.

- **SYNC** SYNC Signal: The signal is used to indicate the start of the 56-bit processor cycle. It is low when the HP41 is in SLEEP mode, SYNC validates instructions in the ISA line. When fetching data or a peripheral is in control SYNC is remains low. Driver circuitry is anticipated for possible future use.

- **ISA** ISA Signal: This line carries the 16-bit address of the ROM word to be fetched, and the ROM drives this line with the fetched 10-bit instruction word during the end of the cycle.

- F1 F1/FIN, FLAG IN signal: This line triggers the HP41 when peripherals want to interrupt the system. Driver circuitry is anticipated for possible future use.

- **DATA** Data Signal: This line is the serial input/output of CPU data, and typically reflects the contents of the CPU C-register. It is used by the MLDL for determining data and address for the word to be written to MLDL memory. The DATA signal is driven by the memory or peripheral device when reading data. Driver circuitry is anticipated for possible future use.

- PWO Power On Signal: This line indicates to the system that the CPU is entering RUN mode and can be used for devices to enter power down mode when the signal is low in combination with SYNC. The HP41 is in SLEEP mode (switched off) when both PWO and SYNC are low. It is in STANDBY mode when PWO is low and SYNC is high.

- **GND** Ground: Referral to system Ground.

- **B3** B3: Used in combination with B4 to determine the port address. B3 is high in ports 2 and 4, not connected in ports 1 and 3. B3 is not used on the MLDL2000 as the device is totally ignorant of the port it is plugged in.

- V+ V+ is the system power signal at +6.5V, up to 20 mA in RUN and STANDBY mode. It drops to battery voltage in SLEEP mode.

**B4** B4: Used in combination with B3 to determine the port address. B4 is high in ports 3 and 4, not connected in ports 1 and 2. B3 and B4 are not used on the MLDL2000 as the device is totally ignorant of the port it is plugged in.

| BAT | BAT is a diode isolated line to the HP41's battery, and may be |

|-----|----------------------------------------------------------------|

|     | used for devices drawing higher current. The line is always    |

|     | connected to the battery PLUS terminal.                        |

#### Usage of B3/B4

Note that 0 means not connected, and 1 means connected to Vcc. A pull down resistor is required for correct logical levels.

| B4 | B3 | Port | Decoded Address Range |

|----|----|------|-----------------------|

| 0  | 0  | 1    | \$8000-\$9FFF         |

| 0  | 1  | 2    | \$A000-\$BFFF         |

| 1  | 0  | 3    | \$C000-\$DFFF         |

| 1  | 1  | 4    | \$E000-\$FFFF         |

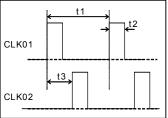

## **Signal Timing Description**

The HP41 Signal Timing is shown in the figure, and has a number of phases. The timing will only be described with respect to the relevance for the MLDL2000 and the user is encouraged to use other sources for a more elaborate description of the HP41 interface. The total Instruction Cycle Time for the original HP41C is about 160 µs (6300 instructions per second). Timing is measured in December 2002 on an HP41C (appr. 2 times speedup) and an HP41CX (no speedup). Exact timing may vary between individual machines. The CLK duty cycle is approximately 20%. An overview of the HP41 instruction cycle can be found in the appendix.

|                      |              | Original HP41 | Appr. 2* Speed-up |

|----------------------|--------------|---------------|-------------------|

| instructions/second  |              | 6400          | 9400              |

| instruction cycle    | Sync-to-sync | 156.8 µs      | 106.4 µs          |

| clock cycle          | T1           | 2. 8 µs       | 1.9 µs            |

| clock frequency      |              | 357 kHz       | 526 kHz           |

| clock pulse width    | T2           | 0.6 µs        | 0.38 µs           |

| CLK01 to CLK02 delay | T3           | 1.04 µs       | 0.72 µs           |

# MLDL2000 Operation

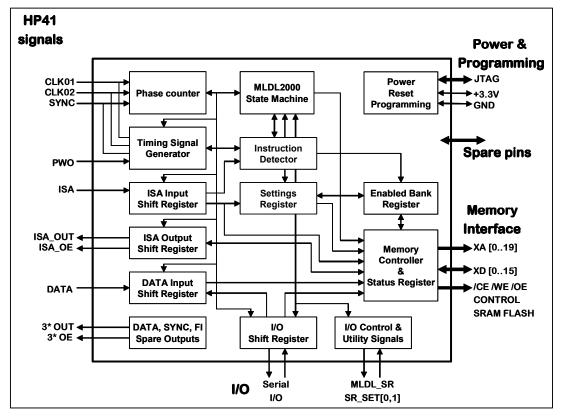

See the block diagram on page 3 for a high level overview. The exact pin-out is listed in Appendix B. The MLDL2000 is divided in the following logical blocks:

#### 1. Input and Output buffers and level shifter

Buffers and level shifters are required to interface the 3.3V based CPLD with the HP41. The CPLD I/O's are 5V tolerant, but the HP41 power and signals are typically around 6.5V and that is above the maximum rating of the CPLD. The DATA

and SYNC lines are implemented as bidirectional signals, and FI as an output. The MLDL2000 is not driving DATA, SYNC or FI and the corresponding Output Enables are always driven high. This may be used in future upgrades.

#### 2. Power Regulator

Generates the 3.3V power for the CPLD and memory devices. In addition it supports circuitry for switching a backup battery for maintaining the contents of the SRAM on power down.

### 3. Phase Counter and Timing Logic (internal in CPLD)

The serial bus of the HP41 needs a reference for the start of the 56-bit processor cycle, and the end of the SYNC signal serves this function. Due to the design of the Phase Counter in the MLDL2000 the number assigned to the phases is shifted by one clock. The MLDL Phase Counter is a 6-bit counter that resets at phase #55 (670), as SYNC may not always be present (SYNC indicates an instruction being fetched, if there is no SYNC it is a read of data). The actual reset of the Phase Counter is done by latching subsequent (SYNC and CLK01) followed by (SYNC low and CLK01). Various events are indicated by the Phase Counter. Note that in the description the 'real' phase numbers are used, the phases as used in the MLDL VHDL design files are all one less due to the shifting.

The Phase Counter and Timing Logic is critical to the MLDL2000. Most important part are 6-bit phase counter and the SYNC detector. The SYNC detector resets the phase counter after detecting the presence of last falling edge of SYNC. Since SYNC may not be present at all times the SYNC detector also resets the phase counter if the count of 670 is reached. The ph\_reset signal is an asynchronous reset for the phase counter. Some other logic and registers are used to indicate the various states of the MLDL2000, to facilitate control of the main state machine.

#### 4. Instruction Detector: I\_STAT (internal in CPLD)

The Instruction Decoder is responsible for recognizing one of the supported instructions in the MLDL. Specific instructions may be defined here to allow I/O operations to user defined I/O or to communicate with the PC interface. Other options may exist to control the Settings Registers or to access FLASH and SRAM. The instruction decoder only operates when SYNC was present during the instruction fetch. If no SYNC was present then the 'instruction' might have been data or the second part of a branch instruction. The Instruction Detector controls the state of I Stat:

| I_IDLE   | _                          | default state, returns to I_IDLE on start of ISA Address (phase 17 octal) |

|----------|----------------------------|---------------------------------------------------------------------------|

| I_WROM   | \$040                      | write data in C[2:0] to address in C[6:3] (only in RAM version) or to I/O |

| I_FETCH  | \$330                      | read data from ROM address in C[6:3] to C[2:0]                            |

| I_ENBANK | \$100, \$180, \$140, \$1C0 | enable ROM bank 1, 2, 3 or 4 for current device                           |

#### 5. Enabled Bank Registers: EBR (internal in CPLD or in SRAM)

The EBR store information about the current active bank. Bank Switching is described in a separate paragraph.

#### 6. ISA Input Shift Register: ISR (internal in CPLD)

The ISR reads the ISA line into a shift register for decoding the address and the instruction to act upon. When the external interface is enabled (assertion of /X\_EN) the ISA Input Shift Register is used for the serial I/O data stream. The first task in the MLDL design is to determine the address of the instruction to be fetched. This is done by moving the data on ISA (starting at phase #16) to the ISA Shift Register (ISR) and using the 4 most significant address bits (which is the HP41 Port Address) to access the SR in combination with the currently selected Bank (2 bits).

An 10-bit word is returned by the SR, which indicates where in the MLDL2000 memory map the ROM block is located and if it is SRAM, FLASH or IO and if the Port/Bank combination is enabled at all. In addition, SRAM might be write-protected.

Having read the 10-bit word from SR, the data is used in combination with the 12 least significant address bits to address the appropriate location in EPROM, SRAM or I/O.

#### 7. Data Input Shift Register: DSR (internal in CPLD)

The Data Input Shift Register takes the HP41 DATA line and extracts information from it for the WROM instruction. D0-D9 contains the 10-bit instruction, D12-27 carries the 16-bit address. The DATA line is used only during the WROM and FETCH instructions and contains the address and the instruction to be written to the indicated location in MLDL memory. During the WROM instruction the DATA line is used as follows:

- D00..09 Instruction to be written (lowest 10 bits of DATA in S&X), where D0 is LSB of data

- D12..27 Address to write Instruction to (lowest bits of Mantissa), where D12 is LSB of address

D28..31 Spare bits for direct addressing of MLDL2000 memory and used by the I/O Interface

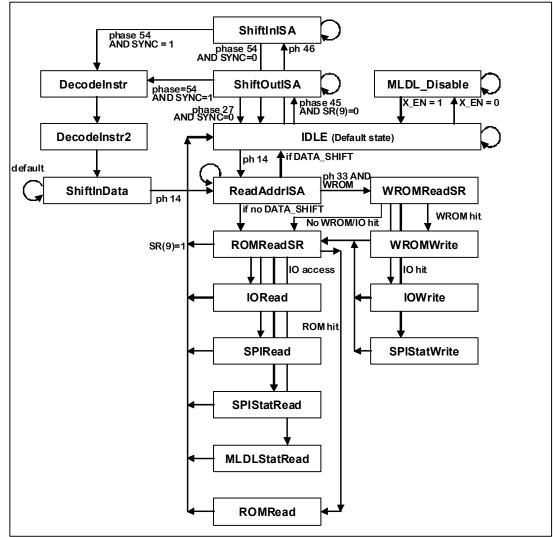

The WROM instruction sets up the MLDL for programming an SRAM location based on information that is present on the DATA line. For future additions a DATA Output with driver is available but currently not in use. The DSR is used as shift register for I/O operations when /X\_EN is asserted to allow access to SRAM and FLASH through the I/O interface. 8. Main State Machine: MLDL\_STAT (internal in CPLD)

The Main State Machine is the heart and soul of the MLDL2000. Using various signals from the Phase Counter and Timing Logic is determines when and what actions should be taken for interfacing with memory and when data has to be shifted in or out. Most other blocks use the state output of this block for control.

The phase timing of the different states may vary, depending on the previous state. This allows for a much more flexible and straightforward state machine implementation (in a VHDL Finite State Machine). Note that IDLE does not mean that the MLDL has nothing to do, as various operations are in parallel to the Main State Machine, for example the timing of the DATA Shift Register and ISA Input Shift Register, but these are not under direct control of the Main State Machine. The states SPIRead, SPIStatRead and SPIStatWrite are there for compatibility with V2 of the MLDL2000.

#### 9. Settings Register: SR (internal in CPLD)

The Settings Register reads and stores the results of the access to the SR's in FLASH or SRAM to determine if and how an HP41 ROM (or RAM) page should be accessed.

#### 10. ISA Output Shift Register: OSR (internal in CPLD)

Transfers parallel data from (FLASH or SRAM) memory as output to the HP41 on the ISA line. This block has a direct interface with the external data bus.

#### 11. Memory Access Logic (internal in CPLD)

The Memory Access Logic controls the external memory devices FLASH and SRAM. It is an 20-bit wide address and 16-bit wide data bus, with separate chip enable, write enable and output enable for external devices. The Memory Access Logic is the largest piece of logic in the MLDL2000. Every state of MLDL\_STAT that demands a memory access is handled in this block. Manipulation of the various address and data lines are described later. Due to the operation of the Main State Machine the memory access cycles may not always be in the same clock phase.

| Version 1.51            |  |  |  |

|-------------------------|--|--|--|

| <b>Meindert Kuipers</b> |  |  |  |

#### 12. FLASH (Non Volatile Flash Memory)

Non Volatile Flash Memory replaces the traditional EPROM's on the MLDL. A Flash programming interface will be provided through the IO Interface, as Flash programming through the HP41 interface is probably not an option due to the strict timing requirements for programming. The FLASH contains both the ROM images and Settings Registers, and the Memory Map layout will be described later. The FLASH memory is a 3.3V single voltage device that does not require any special programming voltages.

#### 13. SRAM (Non Volatile Battery Backed Static Memory)

SRAM is used for storing user developed ROM images in combination with Settings Registers. Data may be written to the SRAM by the HP41 by means of the WROM (\$040) instruction.

#### 14. SR (Settings Registers) (in FLASH and SRAM memory)

The Settings Registers contain the memory layout of the MLDL, i.e. which ROM bank can be found on which memory location in either FLASH or SRAM, and if the ROM is enabled at all. The SR can be in SRAM or FLASH, depending on the setting of an external input. This is done mainly to prevent unexpected behavior of the MLDL when the SRAM is empty or corrupted (for example after battery failure or exchange). Four sets of SR are supported in both FLASH and SRAM.

#### 15. IO Shift Register: IOR (internal in CPLD)

The Input/Output Interface Logic can be used to communicate with the outside world and offers a serial interface port using a simple protocol. The I/O Interface is described in more detail in a separate chapter. The IO Interface is memory mapped in one of the (Bank switched) HP41 ROM spaces, as this is easiest to implement. Memory mapped I/O is chosen to make the MLDL totally independent and not to having to rely on certain ROM contents or instructions. A separate part of the IO Interface Logic is used to control the MLDL2000 itself and allows reading, writing, erasing and programming of SRAM, FLASH and SR through the external interface that can be controlled from the parallel port of a PC or any other device that supports free control of a number of digital I/O lines.

#### 16. JTAG Programming Interface

A JTAG interface is provided to enable programming of the CPLD logic. A special programming cable (supplied by Xilinx or third parties) with software should be used to (re-)program the CPLD. It is also possible to program the CPLD through the USB Interface (not supported in the Beta version). The JTAG pins are shared with some pins of the External I/O Interface.

#### 17. Spare I/O pins

A number of pins that are unused on the CPLD are routed to pads on the MLDL2000 PCB. These may be used for debugging or future or custom applications.

### MLDL memory layout

Purpose of the MLDL is to be as flexible as possible, and enable as much possibilities as is practical. This means that the settings of the MLDL will be somewhat complicated and that these settings will have to be programmable from the HP41 itself as well as from the external interface.

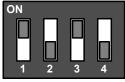

The MLDL2000 has two external devices which are controlled by their own Chip Select and Enable lines: FLASH and SRAM. The Settings Registers are embedded in either the FLASH or SRAM. An external switch indicates if SRAM or FLASH is to be used for the SR by selecting the MLDL\_SR input. In addition, signals SR\_SET[0..1] enable to choose 1 out 4 sets of Settings Registers to allow fast switching between different configurations. It is strongly recommended to use one of the configurations with a minimum setting to recover from lock-up situations (for example after use of the Service ROM), and possibly another set to completely disable the MLDL2000. A 4<sup>th</sup> signal, MLDL\_DIS, is used to disable all output from the MLDL2000 to the HP41, for example when initializing the MLDL2000.

To access the devices a 20-bit address bus (XA, for eXternal Address) is used with the 16-bit XD (eXternal Data). The top block of FLASH and SRAM is used to store the Settings Registers. Of the 16 data bits only the 10 least significant bits are actually used.

The SRAM memory above \$40000 can not be used for storing ROM images, as the SR's do not allow usage of address lines A18 and A19. The SR's are stored in SRAM starting at address \$7FF00. The I/O interface allows direct access to this area for specific applications. Possible future expansions of the MLDL2000 could include access of the SRAM area above \$40000 for emulation of user registers.

The FLASH device used is the AM29LV160DB, with a sector size of 32K words (good for 8 ROM images each). The lowest 4 blocks are boot blocks and have smaller sector sizes (see table). Since there is plenty of room in the FLASH memory it is advised to spread the ROM images as much as possible to allow erasing of only a single ROM image. Best practice is to collect all ROMS that will never change (like copies of the original ROMS) together in FLASH sectors, and spread out those that are more likely to change.

The Settings Registers are all in one sector of the FLASH memory. Changing a value may require erasing and reprogramming of the entire sector! It is therefore best not to keep any ROM images in the sector of the Settings Registers.

Each of the individual 10-bit Settings Registers has the following layout:

|       | Setting Register Layout |       |       |       |       |       |       |       |       |

|-------|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 9 | Bit 8                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| EN    | FL/SR=1                 | 10    | WP    | A17   | A16   | A15   | A14   | A13   | A12   |

| EN    | FL/SR=0                 | A19   | A18   | A17   | A16   | A15   | A14   | A13   | A12   |

Bit 9: EN, Enable

0 = FLASH/SRAM/IO Bank is enabled Bit 8: FL/SR: Flash or SRAM 1 = FLASH/SRAM/IO Bank is disabled

18: FL/SR: Flash or SRAM0 = ROM Image is in FLASH

1 = ROM Image is in SRAM

If Bit 9 is 0 (ROM Image is in FLASH) then Bit 5 to 0 have the following meaning: Bit 7-0: A19-12 for addressing the FLASH memory (or the ROM image number)

If Bit 8 is 1 (ROM Image is in SRAM) then Bit 5 to 0 have the following meaning:

Bit 7: IO, I/O Interface

0 = Bank is SRAM 1 = Bank is IOI

Bit 6: WP: Write Protect (for SRAM only, not for I/O)

0 = Write Enabled 1 = Write Protected

Bit 5-0: A17-12 for addressing the SRAM memory (or the ROM image number)

If Bit 8 is 1 and Bit 7 is 1 (I/O Interface) then bit 6 indicates if the image is mapped in SRAM or FLASH. The block can therefore not be write protected. When the image is in FLASH, it can only be located in the first 64 blocks of FLASH (FLASH 0-63, addresses \$00000-\$3FFFF.

Bit [9-8-7] = '1-1-1' (I/O Bank)

Bit 6: 0 = ROM mapped in FLASH 1 = ROM mapped in SRAM

- **NOTE 1**: For writing, an SRAM bank does not have to be enabled (bit 0) to allow initializing memory but it must be Write Enabled.

- **NOTE 2**: SRAM banks that do not exist in an HP41 memory map must be write protected, and all Setting Registers must be initialized at meaningful values to prevent overwriting existing memory contents.

- **NOTE 3**: It is possible to have different SR's point to the same ROM bank, although this might give unexpected results. This would be the same as plugging identical modules in multiple ports.

**NOTE 4**: Although multiple IO banks are possible, these all alias to the same physical I/O interface and registers for accessing SRAM and FLASH.

- **NOTE 5**: A disabled bank is best indicated with \$3FF in the SR. This allows for non-initialized FLASH to be used as SR that can be reprogrammed without first erasing the whole block.

- NOTE 6: FLASH memory is erased by sector, and a sector may contain multiple ROM images and/or Setting Register sets.

- **NOTE 7**: FLASH memory bits can only be programmed from '1' to '0'. An erase operation (of a complete sector) is required to set bits from '0' to '1'.

- **NOTE 8**: An I/O block cannot be write protected when it is in SRAM.

- NOTE 9: An I/O block can only be mapped in the first 64 blocks of FLASH.

The switch has the following layout. Note that when **ON** the respective input is connected to GND. When **OFF** the input is pulled up by the internal pullup resistors.

| Switch 1<br>Switch 2 | MLDL_DIS<br>MLDL_SR | OFF:<br>OFF: |   |            | MLDL Disabled<br>SR from FLASH | <i>ON</i> :<br><i>ON</i> : | MLDL Enabled<br>SR from SRAM |

|----------------------|---------------------|--------------|---|------------|--------------------------------|----------------------------|------------------------------|

| Switch 3-4           | SR SET[1,0]         | OFF          | - | <b>OFF</b> | SR Set 0, base \$FFF00 (FLAS   | 5H), \$7FF                 | F00 (SRAM)                   |

|                      |                     | <b>OFF</b>   | - | ON         | SR Set 1, base \$FFF40 (FLAS   | SH), \$7FF                 | F00 (SRAM)                   |

| ON                   |                     | ON           | - | <b>OFF</b> | SR Set 2, base \$FFF80 (FLAS   | SH), \$7FF                 | F00 (SRAM)                   |

|                      |                     | ON           | - | ON         | SR Set 3, base \$FFFC0 (FLAS   | SH), \$7F                  | F00 (SRAM)                   |

# **Detailed Memory Map**

| F     | FLASH Memory Layout |                                 |  |  |  |  |

|-------|---------------------|---------------------------------|--|--|--|--|

| Start | End                 | Contents                        |  |  |  |  |

| FFF00 | FFFFF               | SECTOR 34<br>Settings Registers |  |  |  |  |

| F8000 | FEFFF               | SECTOR 34, ROM 248-254          |  |  |  |  |

| F0000 | F7FFF               | SECTOR 33, ROM 240-247          |  |  |  |  |

| E8000 | EFFFF               | SECTOR 32, ROM 232-239          |  |  |  |  |

| E0000 | E7FFF               | SECTOR 31, ROM 224-231          |  |  |  |  |

| D8000 | DFFFF               | SECTOR 30, ROM 216-223          |  |  |  |  |

| D0000 | D7FFF               | SECTOR 29, ROM 208-215          |  |  |  |  |

| C8000 | CFFFF               | SECTOR 28, ROM 200-207          |  |  |  |  |

| C0000 | C7FFF               | SECTOR 27, ROM 192-199          |  |  |  |  |

| B8000 | BFFFF               | SECTOR 26, ROM 184-191          |  |  |  |  |

| B0000 | B7FFF               | SECTOR 25, ROM 176-183          |  |  |  |  |

| A8000 | AFFFF               | SECTOR 24, ROM 168-175          |  |  |  |  |

| A0000 | A7FFF               | SECTOR 23, ROM 160-167          |  |  |  |  |

| 98000 | 9FFFF               | SECTOR 22, ROM 152-159          |  |  |  |  |

| 90000 | 97FFF               | SECTOR 21, ROM 144-151          |  |  |  |  |

| 88000 | 8FFFF               | SECTOR 20, ROM 136-143          |  |  |  |  |

| 80000 | 87FFF               | SECTOR 19, ROM 128-135          |  |  |  |  |

| 78000 | 7ffff               | SECTOR 18, ROM 120-127          |  |  |  |  |

| 70000 | 77FFF               | SECTOR 17, ROM 112-119          |  |  |  |  |

| 68000 | 6FFFF               | SECTOR 16, ROM 104-111          |  |  |  |  |

| 60000 | 67FFF               | SECTOR 15, ROM 96-103           |  |  |  |  |

| 58000 | 5FFFF               | SECTOR 14, ROM 88-95            |  |  |  |  |

| 50000 | 57FFF               | SECTOR 13, ROM 80-87            |  |  |  |  |

| 48000 | 4FFFF               | SECTOR 12, ROM 72-79            |  |  |  |  |

| 40000 | 47FFF               | SECTOR 11, ROM 64-71            |  |  |  |  |

| 38000 | 3ffff               | SECTOR 10, ROM 56-63            |  |  |  |  |

| 30000 | 37FFF               | SECTOR 09, ROM 48-55            |  |  |  |  |

| 28000 | 2FFFF               | SECTOR 08, ROM 40-47            |  |  |  |  |

| 20000 | 27FFF               | SECTOR 07, ROM 32-39            |  |  |  |  |

| 18000 | 1FFFF               | SECTOR 06, ROM 24-31            |  |  |  |  |

| 10000 | 17FFF               | SECTOR 05, ROM 16-23            |  |  |  |  |

| 08000 | OFFFF               | SECTOR 04, ROM 08-15            |  |  |  |  |

| 04000 | 07FFF               | SECTOR 03, ROM 04-07            |  |  |  |  |

| 03000 | 03FFF               | SECTOR 02, ROM 03               |  |  |  |  |

| 02000 | 02FFF               | SECTOR 01, ROM 02               |  |  |  |  |

| 00000 | 01FFF               | SECTOR 00, ROM 00-01            |  |  |  |  |

| :     | SRAM Memory Layout |                    |  |  |  |  |

|-------|--------------------|--------------------|--|--|--|--|

| Start | End                | Contents           |  |  |  |  |

| 7FF00 | 7ffff              | Settings Registers |  |  |  |  |

| 70000 | 7feff              | Reserved           |  |  |  |  |

| 60000 | 6FFFF              | Reserved           |  |  |  |  |

| 50000 | 5FFFF              | Reserved           |  |  |  |  |

| 40000 | 4FFFF              | Reserved           |  |  |  |  |

| 30000 | 3FFFF              | ROM 48-63          |  |  |  |  |

| 20000 | 2FFFF              | ROM 32-47          |  |  |  |  |

| 10000 | 1FFFF              | ROM 16-31          |  |  |  |  |

| 00000 | OFFFF              | ROM 00-15          |  |  |  |  |

| _              | SETTINGS REGISTERS<br>MEMORY LAYOUT |        |  |  |  |  |

|----------------|-------------------------------------|--------|--|--|--|--|

| ADDR           | HP41 Port                           | Bank   |  |  |  |  |

| FFFFF          | F                                   | 3      |  |  |  |  |

| FFFFE          | F                                   | 2      |  |  |  |  |

| FFFFD          | F                                   | 1      |  |  |  |  |

| FFFFC          | F                                   | 0      |  |  |  |  |

| FFFFB          | E                                   | 3      |  |  |  |  |

| FFFFA          | E                                   | 2      |  |  |  |  |

| FFFF9          | E                                   | 1      |  |  |  |  |

| FFFF8          | E                                   | 0      |  |  |  |  |

| FFFF7          | D                                   | 3      |  |  |  |  |

| FFFF6          | D                                   | 2      |  |  |  |  |

| FFFF5          | D                                   | 1      |  |  |  |  |

| FFFF4          | D                                   | 0      |  |  |  |  |

| FFFF3          | С                                   | 3      |  |  |  |  |

| FFFF2          | С                                   | 2      |  |  |  |  |

| FFFF1          | С                                   | 1      |  |  |  |  |

| FFFFO          | С                                   | 0      |  |  |  |  |

| FFFEF          | В                                   | 3      |  |  |  |  |

| FFFEE          | В                                   | 2      |  |  |  |  |

| FFFED          | В                                   | 1      |  |  |  |  |

| FFFEC          | В                                   | 0      |  |  |  |  |

| FFFEB          | A                                   | 3      |  |  |  |  |

| FFFEA          | A                                   | 2      |  |  |  |  |

| FFFE9          | A                                   | 1      |  |  |  |  |

| FFFE8          | A                                   | 0      |  |  |  |  |

| FFFE7          | 9                                   | 3      |  |  |  |  |

| FFFE6          | 9                                   | 2      |  |  |  |  |

| FFFE5          | 9                                   | 1      |  |  |  |  |

| FFFE4          | 9                                   | 0      |  |  |  |  |

| FFFE3          | 8                                   | 3      |  |  |  |  |

| FFFE2          | 8                                   | 2      |  |  |  |  |

| FFFE1          | 8                                   | 1      |  |  |  |  |

| FFFEO          | 8                                   | 0      |  |  |  |  |

| FFFDF          | 7                                   | 3      |  |  |  |  |

| FFFDE          | 7                                   | 2      |  |  |  |  |

| FFFDD          | 7                                   | 1      |  |  |  |  |

| FFFDC          | 7                                   | 0      |  |  |  |  |

| FFFDB          | 6                                   | 3      |  |  |  |  |

| FFFDA          | 6                                   | 2      |  |  |  |  |

| FFFD9          | 6                                   | 1      |  |  |  |  |

| FFFD8          | 6                                   | 0      |  |  |  |  |

| FFFD7          | 5                                   | 3      |  |  |  |  |

| FFFD6          | 5                                   | 2      |  |  |  |  |

| FFFD5          | 5                                   | 1      |  |  |  |  |

| FFFD4          | 5                                   | 0      |  |  |  |  |

| FFFD3          | 4                                   | 3      |  |  |  |  |

| FFFD2<br>FFFD1 | 4<br>4                              | 2<br>1 |  |  |  |  |

| FFFDI          | 4                                   | 0      |  |  |  |  |

|                | 3                                   | 3      |  |  |  |  |

| FFFCF<br>FFFCE | 3                                   | 3      |  |  |  |  |

|                | 3                                   | 4      |  |  |  |  |

| FFFCD          | 3                                   | 0      |  |  |  |  |

| FFFCB          | 2                                   | 3      |  |  |  |  |

| FFFCA          | 2                                   | 2      |  |  |  |  |

| FFFC9          | 2                                   | 1      |  |  |  |  |

| FFFC8          | 2                                   | 0      |  |  |  |  |

| FFFC7          | 1                                   | 3      |  |  |  |  |

| FFFC7<br>FFFC6 | 1                                   | 2      |  |  |  |  |

| FFFC5          | 1                                   | 2<br>1 |  |  |  |  |

| FFFC4          | 1                                   | 0      |  |  |  |  |

| FFFC3          | 0                                   | 3      |  |  |  |  |

| FFFC3<br>FFFC2 | 0                                   | 2      |  |  |  |  |

| FFFC1          | 0                                   | 1      |  |  |  |  |

| FFFC0          | 0                                   | 0      |  |  |  |  |

| 11100          | 5                                   | 5      |  |  |  |  |

Above is configuration: SR\_SET(0) = 0, SR\_SET(1) = 0 SRAM SR from \$7FF00 to \$7FFFF

| SETTINGS REGISTERS BASE<br>SR_SET inputs |         |  |  |

|------------------------------------------|---------|--|--|

| SR_SET[01]                               | SR Base |  |  |

| 00                                       | FFFC0   |  |  |

| 01                                       | FFF80   |  |  |

| 10                                       | FFF40   |  |  |

| 11                                       | FFF00   |  |  |

SR\_Set inputs work for both FLASH and SRAM

NOTE: SRAM only has 64 ROM images. SRAM memory above \$40000 is currently not used. Settings Registers use the top of the memory space, this block can not be used by a ROM image. Maximum 20 address bits are implemented, yielding an address space of \$00000-\$FFFFF. SRAM does not have A19 connected, and the areas above \$7FFFF are aliased with regular addressable area. NOTE: All addresses are hex! NOTE: Some shipped MLDL2000 units have even more SRAM. The extra amount of memory is not used, but may be supported in future upgrades of the MLDL2000 NOTE: Some shipped MLDL2000 units have different FLASH memory IC's than indicated, where the sector layout is different (TOP BOOT BLOCK instead of BOTTOM BOOT BLOCK). This is recognized by the MLDL2000 software, and the correct list of sectors is displayed in the software.

ROMReadSR, at \$FFFC0

same for SRAM and FLASH

### FLASH or SRAM read operation (Typical Instruction Fetch)

| HAxx<br>DAxx<br>SRSx | HP41 Address from ISA (Instruction Fetch), in ISA Shift Register<br>HP41 Address from DATA (WROM operation), in DATA Shift Register<br>SR SET inputs |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| lxx                  | Instruction from DATA (WROM operation)                                                                                                               |

| Px                   | Current Active Bank Pointer (Banks 1, 2, 3 or 4)                                                                                                     |

| XAxx                 | External SRAM/FLASH Address Bus                                                                                                                      |

| XDx                  | External SRAM/FLASH Data Bus                                                                                                                         |

| RAxx                 | Rom start Address inFLASH/SRAM, read from SR                                                                                                         |

| Dx                   | Data Read from FLASH/SRAM                                                                                                                            |

|                      |                                                                                                                                                      |

HP41 Address from ISA HA15 HA14 HA13 HA12 HA11 HA10 HA09 HA08 HA07 HA06 HA05 HA04 HA03 HA02 HA01 HA00

XA19 XA18 XA17 XA16 XA15 XA14 XA13 XA12 XA11 XA10 XA09 XA08 XA07 XA06 XA05 XA04 XA03 XA02 XA01 XA00

1

EN

EN

1

1 /SRS1 /SRS0

FL/SR RA19 RA18

XD09 XD08 XD07 XD06 XD05 XD04 XD03

FL/SR IO WP RA17 RA16 RA15

**HA15**

HA14 HA13

RA17 RA16 RA15

#### Entry in Active Bank Table, addressed from HA[14..12] (Bank Switching in system pages not supported)

Page 8 - 15 P1 P0

XD02 XD01 XD00

RA14 RA13 RA12

**RA12**

RA14 RA13

HA12 P1 P0

| for SRAM and FLASH                               | 1 | 1 | 1 | 1 | 1    |

|--------------------------------------------------|---|---|---|---|------|

| Settings Register Read<br>Base at \$FFF00 (FLASH |   | • |   |   | )1]. |

| ROMRead              | XA19 | XA18   | XA17    | XA16    | XA15 | XA14 | XA13 | XA12 | XA11 | XA10 | XA09 | XA08 | XA07 | XA06 | XA05 | XA04 | XA03 | XA02 | XA01 | XA00 |

|----------------------|------|--------|---------|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| if FLASH             | RA19 | RA18   | RA17    | RA16    | RA15 | RA14 | RA13 | RA12 | HA11 | HA10 | HA09 | HA08 | HA07 | HA06 | HA05 | HA04 | HA03 | HA02 | HA01 | HA00 |

| if SRAM              | 0    | 0      | RA17    | RA16    | RA15 | RA14 | RA13 | RA12 | HA11 | HA10 | HA09 | HA08 | HA07 | HA06 | HA05 | HA04 | HA03 | HA02 | HA01 | HA00 |

| Read data from FLASH |      | Output | Shift R | egister |      | OSR9 | OSR8 | OSR7 | OSR6 | OSR5 | OSR4 | OSR3 | OSR2 | OSR1 | OSR0 |      |      |      |      |      |

External Data Bus if FLASH (FL/SR = 1)

if SRAM (FL/SR = 0)

1 1 1 1

# SRAM write operation (Typical WROM instruction)

| HP41 Address from D                               | ATA[2   | 2712] |        |       | DA15 | DA14 | DA13     | DA12      | DA11   | DA10 | DA09       | DA08           | DA07  | DA06         | DA05         | DA04         | DA03  | DA02         | DA01         | DA00       |

|---------------------------------------------------|---------|-------|--------|-------|------|------|----------|-----------|--------|------|------------|----------------|-------|--------------|--------------|--------------|-------|--------------|--------------|------------|

| Instruction te be writt                           | en fro  | m DA  | TA[09  | 00]   |      |      |          |           |        |      | 109        | 108            | 107   | 106          | 105          | <b>I</b> 04  | 103   | 102          | <b>I</b> 01  | 100        |

| Entry in Active Bank T<br>(Bank Switching in syst |         |       |        |       |      | 12]  |          |           |        |      |            |                |       |              |              |              | Pag   | e 8 - 15     | P1           | P0         |

| VROMReadSR, at \$FFFC0                            | XA19    | XA18  | XA17   | XA16  | XA15 | XA14 | XA13     | XA12      | XA11   | XA10 | XA09       | XA08           | XA07  | XA06         | XA05         | XA04         | XA03  | XA02         | XA01         | XA00       |

| ame for SRAM and FLASH                            | 1       | 1     | 1      | 1     | 1    | 1    | 1        | 1         | 1      | 1    | 1          | 1              | /SRS1 | /SRS0        | DA15         | DA14         | DA13  | DA12         | P1           | P0         |

| Settings Register Read<br>Base at \$ FFF00 (FLAS  |         |       |        |       | )1]. |      | HELAO    |           | 7 – 0) |      | XD09<br>EN | XD08<br>FL/SR  | XD07  | XD06<br>RA18 | XD05<br>RA17 |              | XD03  | XD02<br>RA14 | XD01         | XD0<br>RA1 |

| Base at \$ FFF00 (FLAS                            | п) 01 ‡ |       | 0 (36/ | AIVI) |      |      | if FLASI | · -       | . /    |      |            | FL/SR<br>FL/SR | IO    | WP           | RA17<br>RA17 | RA16<br>RA16 | RA15  |              | RA13<br>RA13 |            |

|                                                   |         |       |        |       |      |      | 1 010 10 |           |        |      | 2.1        | 1 DOIX         | 10    |              | TOTT         | 10110        | 10110 | 10114        | 10110        | Tott       |

| VROMWrite                                         | XA19    | XA18  | XA17   | XA16  | XA15 | XA14 | XA13     | XA12      | XA11   | XA10 | XA09       | XA08           | XA07  | XA06         | XA05         | XA04         | XA03  | XA02         | XA01         | XA0        |

| nly SRAM possible                                 | 0       | 0     | RA17   | RA16  | RA15 | RA14 | RA13     | RA12      | DA11   | DA10 | DA09       | DA08           | DA07  | DA06         | DA05         | DA04         | DA03  | DA02         | DA01         | DA0        |

| Write L8 data to SRAM                             |         |       |        |       |      |      | Externa  | al Data B | Bus    |      | XD09       | XD08           | XD07  | XD06         | XD05         | XD04         | XD03  | XD02         | XD01         | XD0        |

| WITTLE LO UALA LO SINAIN                          |         |       |        |       |      |      |          |           |        |      |            |                |       |              |              |              |       |              |              |            |

# **Bank Switching**

Bank Switching is implemented in the MLDL2000 in a somewhat limited way because Bank Switching is not a function of the HP41 processor, but implemented in the expansion module. As there are various different implementations a generic mechanism is chosen that should support the most common ROMs.

Banks switching in the MLDL2000 uses registers that are located inside the CPLD: Enabled Bank Registers (EBR). This means that the state is forgotten when power is removed from the CPLD, which also happens in *STANDBY* mode. A jumper is provided on the MLDL2000 to allow the user to select the required mode,

Bank Switching is supported only in the ROM pages that are accessible to the user, ROM page \$6 and up. Banks that are in the same port (i.e. the even and odd page) share the same set of EBR's, meaning that switching in an even page will switch banks in the odd page as well. For every set of pages 4 banks are possible. Please be aware of possible conflicts with modules or ROM images that implement bank switching in another way. Bank switching for the internal HP41CX ROMs is not supported.

# External interface

The description of the external interface is for the purpose of documentation only. The CPLD print and USB print (with FT2232 USB controller) should always be used together and it is not recommended that users create their own hardware interfaces.

The MLDL has an external interface for two purposes: to enable initialization, updating and programming the FLASH and SRAM of the MLDL and to provide a means to exchange information with the HP41. The interface is done with a minimum number of signals to keep the interface on the MLDL side as simple as possible, while at the same time providing maximum control of the MLDL settings. The FLASH memory device requires special access cycles for erasing and programming, and therefore it must be possible to have full access to all address-, control- and data lines of the memory devices. A relatively simple serial I/O Interface is defined to communicate with the HP41 with a minimum amount of hardware as this facilitates the 'casual' user. Some of the I/O signals can be connected to the JTAG signals in order to allow programming of the CPLD through the external interface without the need for a special JTAG programming cable.

**NOTE**: Access cycles to the FLASH that are intended to program, erase or perform other commands should follow the exact device specifications.

The I/O Interface supports a serial mode which offers sufficient possibilities to control the MLDL2000 with a wide range of equipment. It is recommended that 3.3V I/O is being used, although the CPLD is 5V tolerant. Care should be taken not to exceed the maximum specified limits of the I/O inputs. For maximum flexibility I recommend using a USB I/O interface as this is very easy to connect to a computer. A USB interface based on the FTDI FT2232C is used and software was written in Delphi to support the basic functionality. This software is available in source code for free under the GNU license. There is a shift register that can be accessed with the serial I/O interface, part of which is implemented using the Data Shift Register (DSR). This means that the MLDL cannot be used during I/O operations for accessing memory. The information is used to drive address and data lines for access to FLASH or SRAM. An additional Command determines what exactly needs to be done: read or write to or from the HP41.

While data is being shifted the MLDL will be disabled under control of the /X\_EN input, because the HP41 cannot not access FLASH or SRAM at the same time. Disabling the MLDL by using the /X\_EN line should only be done when the HP41 is in (light) sleep mode or when turned off to prevent crashes, lockups or other undesirable behavior. It basically switches off all internal clocks and HP41 signal lines into the MLDL2000 to allow full control of the memory interface.

| MLDL pin  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|

| /X_EN     | External Interface Enable, MLDL2000 will be disabled from the perspective of the HP41. This is best done while the HP41 is not active. /X_EN should not be asserted to communicate with the HP41. By default /X_EN is de-asserted. For I/O with the HP41 /X EN should not be asserted.                                                                                                                                                           | in  | active low, 3.3 V  |

| X_DIN     | External Data Input, combined with the JTAG signal TDI.                                                                                                                                                                                                                                                                                                                                                                                          | in  | active high, 3.3 V |

| X_DOUT    | External Data Output, combined with the JTAG signal TDO.                                                                                                                                                                                                                                                                                                                                                                                         | out | active high, 3.3 V |

| /X_CLK    | External Clock, rising edge is used to clock data in or out. The external interface is designed in such a way that data is latched on the rising edge of X-CLK. During a Read command /X_CLK is used to latch data from FLASH or SRAM into output register when /X_STROBE is asserted. /X_CLK is used to assert the /OE or /WE signals and proper timing for the memory devices should be observed. Signal is combined with the JTAG signal TCK. | in  | active low, 3.3 V  |

| /X_STROBE | External Data Strobe, Execute Command. /X_STROBE is used to drive the data lines and /CE signals of the FLASH and SRAM devices on the MLDL2000 and proper timing should be observed. X_STROBE finalizes data transfer in the IOR when writing to the MLDL2000 for HP41 I/O. Signal is combined with the JTAG signal TMS                                                                                                                          | in  | active low, 3.3 V  |

| /X_DAV    | I/O Data Available from HP41 in MLDL, ready for reading when high. The data will<br>already be on the outputs of X_D when /X_OE is asserted. Data should be read with a<br>pulse on /X_CLK or /X_RD, this will reset /X_DAV. /X_DAV is directly connected to<br>H_DAV in the internal MLDL I/O Register for the HP41.                                                                                                                            | out | active high, 3.3 V |

| _ | I/O Data Pending in MLDL, HP41 did not yet read previous written data when high. This signal is directly connected to the H_BSY bit in the internal MLDL I/O Register for the HP41. A read from this register will reset /X_BSY.<br>When /X_EN is asserted (MLDL2000 disabled) /X_BSY reflects the state of the FLASH device's RY-BY signal for easy detection of the end of the FLASH programming or erase cycle. | out | active high, 3.3 V |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|

|   | Program Enable, input for CPLD to enable programming of the CPLD through the<br>external interface instead of having to use the JTAG cable. PE must be low during<br>normal operation and initialization and is high when programming through the JTAG<br>interface is required.                                                                                                                                   | in  | active high, 3.3 V |

When using the external JTAG interface for programming the CPLD, all I/O signals must be in the high-impedance state when the USB interface is used for programming. This can best be guaranteed to program all signals as input when the USB module is used, or to disconnect all lines. PE must driven high to enable the JTAG programming interface. PE is normally low and pulled to ground with a resistor.

For interfacing with the FLASH and SRAM 20 address bits are required, 16 bits of data are required for write operations and a 2-bit command is used. Only the 10 least significant bits are used by the HP41. Data is shifted in first, followed by the 2-bit command and finally the address as shown in the timing diagram below. In a read command data will not be used and does not have to be shifted in. Data is shifted in the IOSR (I/O Shift Register) upon the falling edge of /X\_STROBE.

Assertion of /X\_STROBE will cause the command to be executed and the address in the IOSR to be put on the XA lines. The command is as follows:

| Command | Function        |

|---------|-----------------|

| 00      | Write to Flash  |

| 01      | Write to SRAM   |

| 10      | Read from FLASH |

| 11      | Read from SRAM  |

/X\_EN is used to select between two possible modes: the first one is I/O with the HP41 for use in programs running on the HP41. /X\_EN should be high (de-asserted) when this mode is required. The second mode is when /X\_EN is asserted, and allows direct access to the SRAM and FLASH memory from the external interface. The HP41 can not access any of the MLDL memory when /X\_EN is asserted.

#### Memory Access mode: /X\_EN asserted

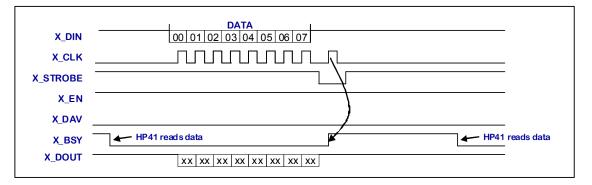

This mode is used to manipulate the memory contents of FLASH and SRAM through the external interface. Note that the HP41 can no longer communicate with the MLDL2000! The I/O is implemented with a USB interface to 'bitbang' the serial interface with two possible commands: read and write. The serial bit stream is shown in the following picture for a Memory Write operation (/X EN is low!):

| X_DIN    | DATA         CMD         ADDRESS           00         01         02         03         04         05         06         07         08         09         10         11         12         13         14         15         F/S         RW         00         01         02         03         04         05         06         07         08         09         10         11         12         13         14         15         F/S         RW         00         01         02         03         04         05         06         07         08         09         10         11         12         13         14         15         F/S         RW         00         01         02         03         04         05         06         07         08         09         10         11         12         13         14         15         16         17         18         19 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X_CLK    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| X_STROBE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| X_EN     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XA[0019] | XA[019]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XD[0009] | XD09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| /CE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| /WE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| /OE      | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Data is shifted in first, then 20 address bits. F/S indicates FLASH or SRAM to be addressed, F/S = 0 means FLASH, F/S = 1 means SRAM. W/R = 0 for a Write operation.

The assertion of /X\_STROBE will activate address, data and /CE lines for the memory device, /X\_CLK will assert the /OE or /WE lines of the selected device. Timing for /X\_STROBE and /X\_CLK should respect the requirements for the specific memory device.

A write operation to FLASH memory does not mean that data is actually written, but rather that a write cycle to the FLASH is done. Writing to FLASH is done by performing a special sequence of write (and sometimes read) operations like the one described above. Please refer to the datasheets of the FLASH memory device (AM29LV160DB) for details. For easy aligning with 8-bit transfers 2 dummy bits and clocks may be inserted before the stream above.

The sequence for reading data from memory is below:

| X_DIN     | CMD         ADDRESS           F/S RW         00         01         02         03         04         05         06         07         08         09         10         11         12         13         14         15         16         17         18         19 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X_CLK_    |                                                                                                                                                                                                                                                                  |

| X_STROBE  |                                                                                                                                                                                                                                                                  |

| X_DOUT    |                                                                                                                                                                                                                                                                  |

| L         |                                                                                                                                                                                                                                                                  |

| XA[0019]— | XA[019]                                                                                                                                                                                                                                                          |

| XD[0009]  |                                                                                                                                                                                                                                                                  |

| /CE       |                                                                                                                                                                                                                                                                  |

| /WE       |                                                                                                                                                                                                                                                                  |

| /OE       |                                                                                                                                                                                                                                                                  |

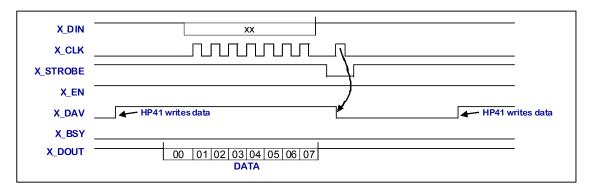

In this case R/W = 1 to indicate a read operation. Data will be latched in the I/O Shift Register upon the falling edge of /X\_CLK when /X\_STROBE is low and will be put on X\_DOUT on every rising edge of /X\_CLK for reading by the external interface. Note that in all cases when /X\_CLK is present data will be shifted in and out, and that this data may not always be meaningful. For easy aligning with 8-bit transfers 2 dummy bits and clocks may be inserted before the stream above.

#### I/O interface

The I/O interface with the HP41 is used for direct data transfer between the HP41 and the outside world. The register can be used without an external command interface and offers a simple handshake mechanism. For practical purposes the I/O register is mapped in the memory space of a ROM as a 10 bits register, with the two highest bits being used for status. Using the I/O interface means that one ROM page is fully reserved for I/O use. The I/O interface is enabled by default when /X\_EN is high.